Команда set_clock_group — это мощная функция проектирования СБИС, которая позволяет инженерам управлять асинхронными, логически и физически исключающими тактовыми сигналами во время синтеза и статического временного анализа (STA). Правильное определение взаимосвязей между тактовыми сигналами критически важно для предотвращения ложных нарушений синхронизации, метастабильности и функциональных ошибок, особенно в многотактовых системах на кристалле (SoC). В этом видео подробно объясняется команда set_clock_group, её применение, практические примеры и важность в цифровом проектировании, временном анализе, синтезе и пересечении доменов синхронизации (CDC).

В этом руководстве мы рассмотрим:

1️⃣ Что такое set_clock_group?

Команда set_clock_group используется в инструментах STA, таких как Synopsys PrimeTime, и инструментах синтеза, таких как Design Compiler или Cadence Genus, для определения асинхронных или исключающих взаимосвязей между доменами синхронизации. Это помогает инструменту определить, какие тактовые сигналы не взаимодействуют логически или физически, обеспечивая точный временной анализ.

2️⃣ Типы группирования тактовых сигналов:

Асинхронные тактовые сигналы: тактовые сигналы без фиксированного фазового соотношения.

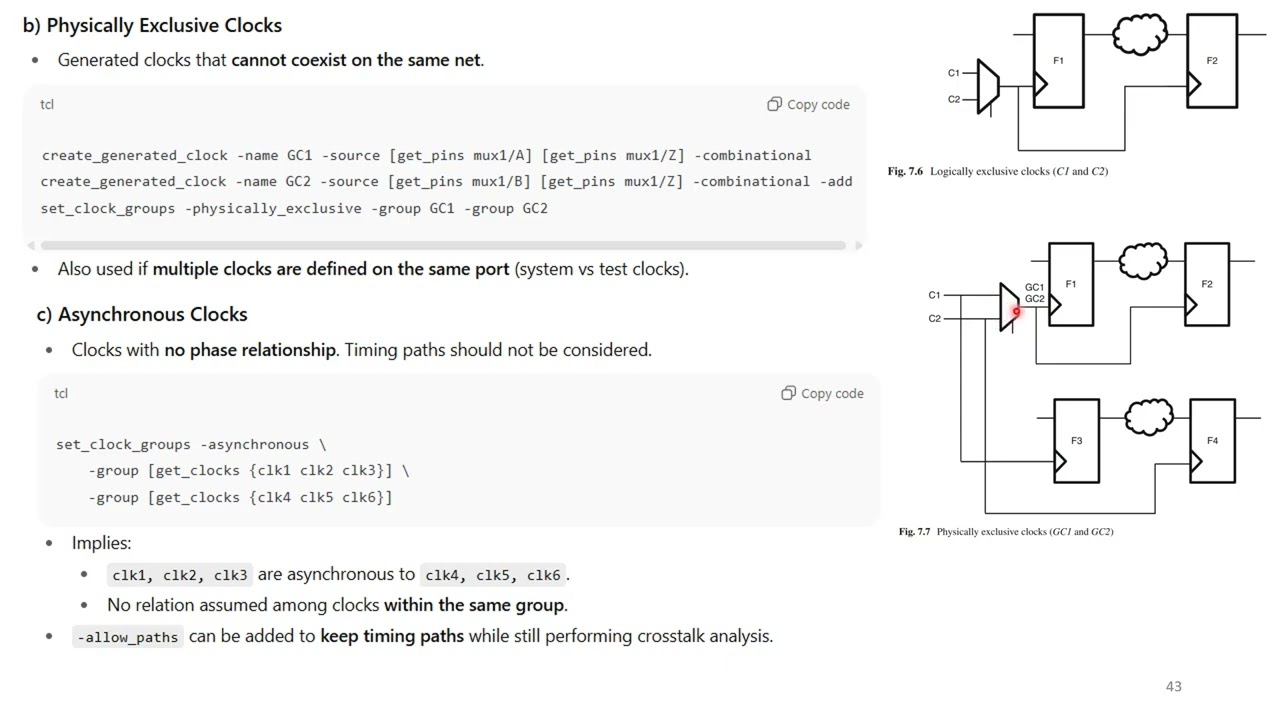

Логически исключающие тактовые сигналы: тактовые сигналы, которые никогда не работают одновременно в проекте.

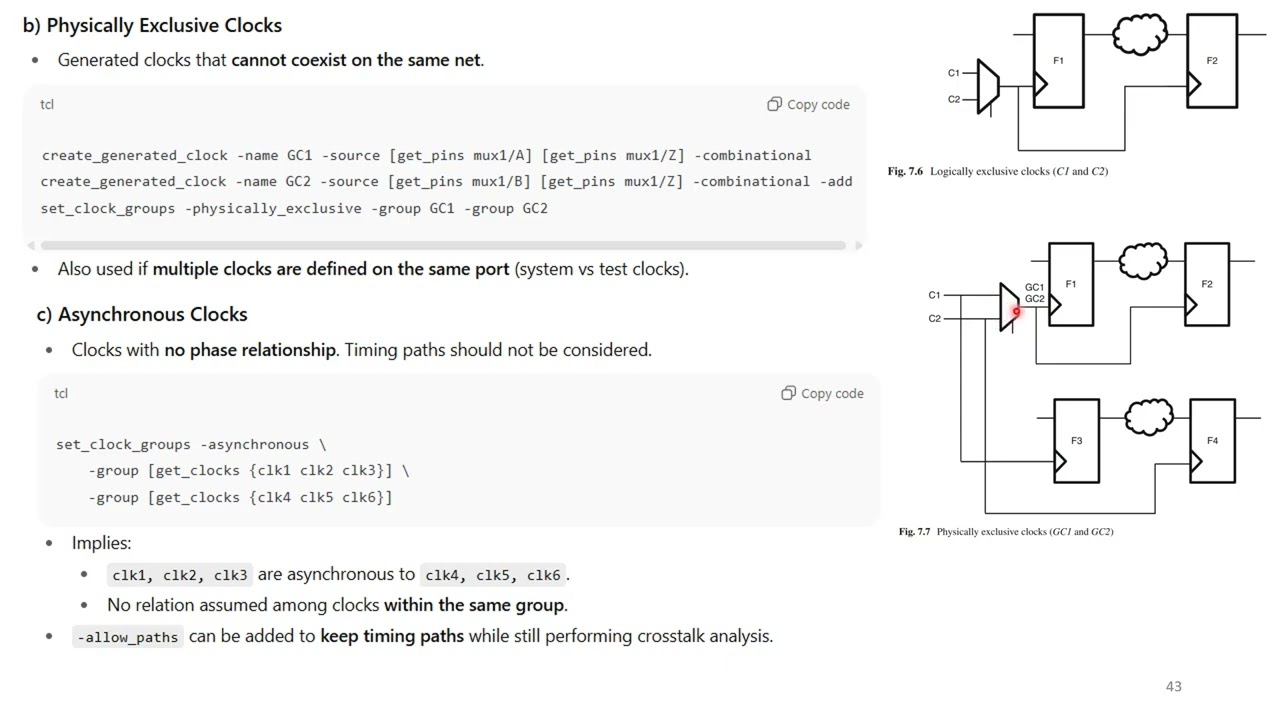

Физически исключающие тактовые сигналы: тактовые сигналы, которые никогда не переключаются одновременно на аппаратном уровне.

В этом видео объясняется, как установить эти соотношения с помощью команды set_clock_group, чтобы избежать ложных нарушений синхронизации.

3️⃣ Практические примеры и варианты использования:

Мы демонстрируем реальные примеры применения set_clock_group в многотактовых схемах. Узнайте, как определять исключающие пути и асинхронные группы тактовых сигналов для упрощения STA и обеспечения надёжного синтеза.

4️⃣ Проблемы в многотактовых схемах:

Неправильное определение групп тактовых сигналов может привести к проблемам с замыканием синхронизации, нарушениям установки/удержания, метастабильности и сбоям синтеза. В этом видео рассматриваются распространённые проблемы и предлагаются решения для безопасной работы с CDC.

5️⃣ Справочники по инструментам для инженеров:

Узнайте, как использовать команду set_clock_group в таких стандартных отраслевых инструментах, как:

Synopsys Design Compiler — во время синтеза RTL

Synopsys PrimeTime STA — для временного анализа

Cadence Genus и Innovus — для синтеза и физической верификации

Почему эта тема важна:

Освоение команды set_clock_group крайне важно для инженеров, работающих над высокопроизводительными цифровыми ИС, системами на кристалле и многотактовыми областями. Правильная группировка тактовых сигналов обеспечивает надёжный временной анализ, точные результаты STA, успешный синтез и снижение количества ошибок после изготовления кристалла. Понимание этой команды обязательно для студентов, инженеров и специалистов, изучающих СБИС, готовящихся к собеседованиям или работающих над сложными цифровыми проектами.

Темы, рассматриваемые в этом видео:

Определение и значение команды set_clock_group в СБИС

Типы групп тактовых сигналов: асинхронные, логически исключающие, физически исключающие

Практические примеры определения групп тактовых сигналов

Обработка пересечений доменов тактовых сигналов (CDC)

Проблемы синтеза и STA для проектов с несколькими тактовыми сигналами

Справочные материалы: Synopsys Design Compiler, PrimeTime, Cadence Genus

Рекомендации по надежному временному анализу и синтезу

💡 Призыв к действию:

Посмотрите это видео, чтобы полностью понять команду set_clock_group, освоить управление несколькими тактовыми сигналами и улучшить свои навыки синтеза и STA. Закрепите свои знания СБИС, избегайте нарушений временных характеристик и обеспечьте успешное завершение проекта в цифровых схемах.

✨ Оставайтесь на связи со мной:

🔗 LinkedIn: / t-maharshi-sanand-yadav

🔗 Instagram: / vlsi.tmsy.tutorials

🎓 Ознакомьтесь с моим курсом на Udemy:

🔗 Проектирование цифровых систем на Verilog HDL: https://www.udemy.com/course/digital-...

✨ Хештеги для охвата:

#tmsytutorials #tmaharshisanandyadav #statictiminganalysis #sta #DTA #vlsi #vlsitraining #chipdesign #synthesis #physicaldesign #PrimeTime #tempus #redhawk #STAtools #DTAtools #STAinVLSI #DTAinVLSI #TimingAnalysis #timingclosure #VLSITutorials #VLSILearning #VLSIInterviewQuestions #VLSICourse #vlsijobs #asic #fpga #vlsidesign #rtldesign #RTLtoGDSII #digitaldesign #Voltus #cadence #synopsys #ansys #designcompiler #genus #Innovus #edatools #socdesign #chipverification #staticanalysis #dynamicanalysis #TimingVerification #STAflow #STAprocess #TimingReports #DelayCalculation #SetupTime #HoldTime #clocktreesynthesis #cts #signalintegrity #PowerAnalysis #IRDrop #EMAnalysis #NoiseAnalysis #GateLevelSimulation #PostLayoutSimulation #FunctionalVerification #RTLVerification #Tim...

Информация по комментариям в разработке